Intel annuncia nuove tecnologie di packaging

Intel ha presentato tecnologie di packaging come EIMB, Foveros, CO-EMIB e OID. Il futuro dei chip è nel package.

Intel, la rinomata azienda di CPU, durante il SEMICON West, ha rilasciato importanti aggiornamenti sulla prossima generazione di CPU Intel e sulle tecnologie adopereranno. Il perno su cui ruoterà tutto è il “package” (intel package): un core è costituito da un die e contenuto nel package. Il die è la sottile piastrina di materiale semiconduttore sulla quale è stato realizzato il circuito elettronico e quest’ultimo è “sigillato in un contenitore”: il package. Dal package fuoriescono i terminali di collegamento (pin), che si innestano nel socket. Il packaging sarà il promotore per la creazione di nuove CPU e combinato con altre tecnologie le prestazioni dei futuri processori miglioreranno notevolmente e ne diminuiranno i consumi in termini di energia.

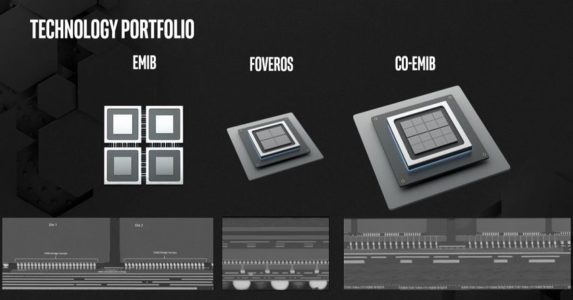

Intel ha poi diversi approcci con cui fa risiedere un numero diversi di die all’interno del package (intel package).

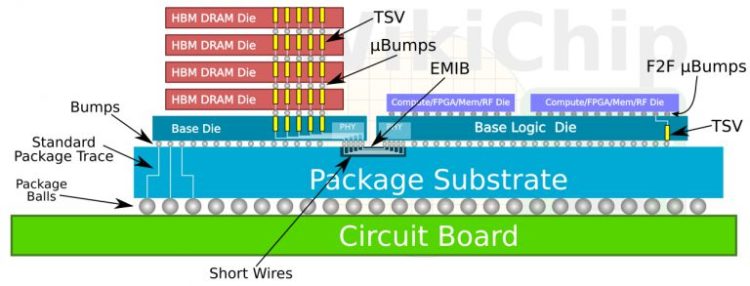

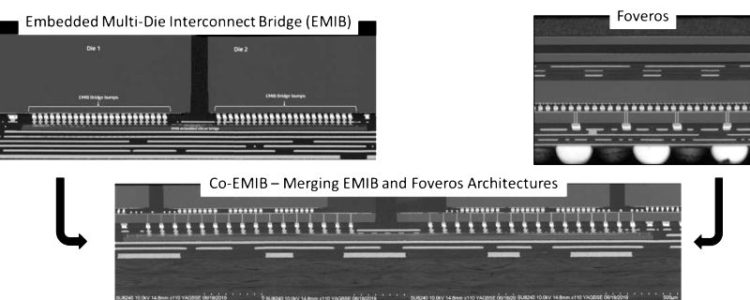

La prima tecnologia utilizzata da Intel fu EMIB (Embedded Multi-Die Ubtercinnect Bridge): un approccio elegante ed economico per l’interconnessione in package di chip eterogenei. EMIB utilizza una specie di “ponte” molto piccolo che offre un’interfaccia chip-to-chip. EMIB è di fatto poi solo un piccolo (quindi economico), pezzo di silicio utilizzato EMIB nello Stratix 10, Agilex FPGA e in Kaby Lake-G.

La seconda tecnologia utilizzata da Intel fu (2018) “Foveros”, che permette a differenti chip destinati per usi diversi di essere impilati uno sopra l’altro e gestire per esempio la cache, il comparto grafico, l’elaborazione o l’AI. Questi chip anche se costituiscono pezzi separati e destinati a funzioni diverse possono essere impilati uno sopra l’altro: il vantaggio di quest’operazione è costituito da una maggiore duttilità e flessibilità computazionale e una larghezza di banda superiore rispetto all’EMIB.

La tecnica che usa Intel è separare quindi la produzione della CPU, della iGPU e di altri elementi prima di assemblarli nel chiplet facendo si che ogni chiplet quindi possa essere realizzato con un processo produttivo differente: la CPU a 10 nm, la GPU a 14 nm e cosi via.

Il succo del discorso è lo sviluppo verticale dei chip mescolando differenti tipi di die, come CPU, iGPU, regolatore del voltaggio ecc… per realizzare SoC (system on chip) personalizzati. Questo permetterà Intel di combinare componenti diversi realizzati con processi produttivi differenti sullo stesso package (intel package).

Importante è capire che “Foveros” non è stato progettato per sostituire EIMB. La tecnologia CO-EIMB è una combinazione della tecnologia Foveros ed EIMB e capito il funzionamento di ambedue queste strutture si avrà un’idea migliore su cosa consiste il CO-EIMB.

Il CO-EIMB consente l’interconnessione orizzontale di due o più Foveros chip. Per rendere chiaro il concetto si può utilizzare una similitudine: il Foveros chip costituisce un grattacielo, il quale è composto da vari piani posti uno sopra l’altro ma secondo l’affermazione precedente vi devono essere due o più Foveros chip quindi due o più grattacieli: questi grattacieli sono quindi collegati tra loro da una skybridge (EIMB).

I vantaggi della tecnologia CO-EIMB è maggiori performance su capacità di calcolo e consumi bassi.

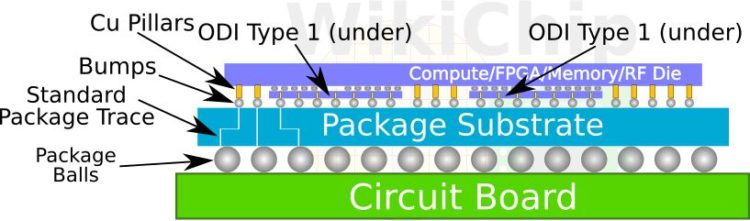

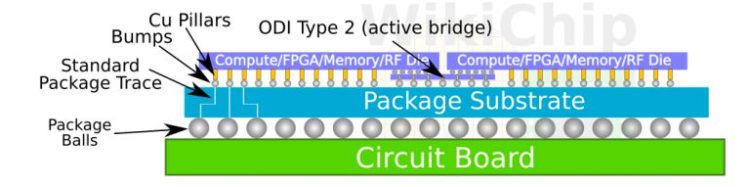

La tecnologia ODI (Omni-Directional interconnect) permette una interconnessione multi-chip e estende l’idea delle tecnologie di EMIB e Fasverous. ODI offre flessibilità e duttilità tra la comunicazione di vari chiplet in un package, e come suggerisce il nome la trasmissione può avvenire sia verticalmente sia orizzontalmente. Il chip superiore può comunicare orizzontalmente con altri chiplet (EMIB technology), ma i chip possono anche interagire verticalmente (come Foveros) attraverso grandi TSVs (trough-silicon vias) che sono creati sia per la produzione di chip che per la creazione di circuiti integrati in 3D. Impilati verticalmente occupano meno spazio e offrono maggiore connettività ma se sono presenti i TSV si ha un package più piccolo e piatto.

ODI offre minore resistenza, basse latenze, un bandwidth più alto e un’erogazione di energia maggiore (e dallo strato di package inferiore attraverso a questi collegamenti verticali è possibile un passaggio di energia verso i chiplet superiori). La superficie per i transistor è più ampia (a causa dei TSV impilati verticalmente) ottimizzando le dimensioni del die.

Nel tipo 1 ODI sarà incorporato sotto il die e potrebbe richiedere diversi ODI per il coretto funzionamento.

Il tipo 2 utilizza la tecnologia EMIB, dove ODI funge da “ponte” per i due die.

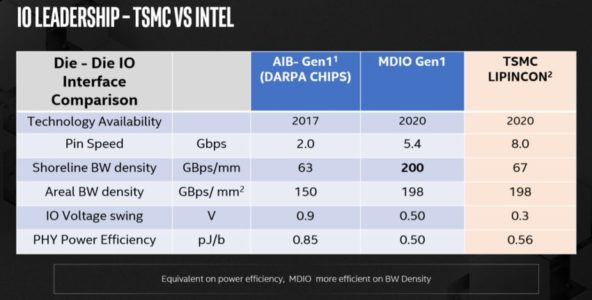

Intel nel SEMICON West ha annunciato il successore dell’attuale AIB (advanced Interface bus) ed è MDIO (management data input/output). MDIO è un’interfaccia “die to die” che svolgerà un ruolo importante per Intel e debutterà nel 2020 e avrà una migliore efficienza energetica, facendo si che il pin speed passi da 2.0 a 5.4 GBps/mm.

Nessuna di queste tecnologie avrà un impatto diretto sull’acquisto di queste CPU sui futuri PC. ODI rappresenta una sfida per Intel e potrà confermare o confutare la legge di Moore.